diff --git a/docs/.vuepress/sidebar.js b/docs/.vuepress/sidebar.js

index 990850f..741d425 100755

--- a/docs/.vuepress/sidebar.js

+++ b/docs/.vuepress/sidebar.js

@@ -19,7 +19,8 @@ const sidebar = {

'/doc/board/stm32f407zgt6',

'/doc/board/hifive1-rev',

'/doc/board/maxgo',

- '/doc/board/kd233'

+ '/doc/board/kd233',

+ '/doc/board/nexys'

],

'controller': [

'/doc/controller/ximenzi',

diff --git a/docs/doc/board/README.md b/docs/doc/board/README.md

index bfdc3d4..d6fac90 100644

--- a/docs/doc/board/README.md

+++ b/docs/doc/board/README.md

@@ -15,3 +15,5 @@

* [MAXGO](/doc/board/maxgo.md)

* [KD233](/doc/board/kd233.md)

+

+* [Nexys_A7-100T](/doc/board/nexys.md)

diff --git a/docs/doc/board/nexys.md b/docs/doc/board/nexys.md

new file mode 100644

index 0000000..47e315d

--- /dev/null

+++ b/docs/doc/board/nexys.md

@@ -0,0 +1,76 @@

+# Nexys A7-100T

+

+## 综述

+

+

+  +

+

+ Nexys A7

+

+

+Nexys A7-100T 是 Digilent 多孔 RAM-based Nexys 开发板的简易替代品。搭载Xilinx®Artix™-7 FPGA芯片,Nexys 4 DDR 是一个打开即用型的数字电路开发平台,帮助使用者能够在课堂环境下实现诸多工业领域的应用,配有高容量的大型FPGA芯片(Xilinx产品编号XC7A100T-1CSG324C)并集成了USB,以太网和其它端口。Nexys 4 DDR开发板能实现从理论型组合电路到强大的嵌入式处理器的多种设计。

+## 硬件特点

+

+

+

+| 序号 | 描述 | 序号 | 描述 |

+| ---- | ---- | ---- | ---- |

+| 1 | 选择供电跳线 |13|CPU复位按键(用于软核)|

+| 2 | UART/JTAG共用USB接口 |14|FPGA 配置复位按键|

+| 3 | 外部配置跳线柱(SD/USB) |15|模拟信号Pmod端口(XADC)|

+| 4 | Pmod端口 |16|编程模式跳线柱|

+| 5 | 扩音器 |17|音频连接口|

+| 6 | 电源测试点 |18|VGA连接口|

+| 7 | 16个LED |19|FPGA编程完成LED|

+| 8 | 16个按键开关 |20|以太网连接口|

+| 9 | 8位7段数码管 |21|USB连接口|

+| 10 | 可选用与外部接线的JTAG端口 |22|(工业用)PIC24编程端口|

+| 11 | 5个按键开关 |23|电源开关|

+| 12 | 板载温度传感器 |24|电源接口|

+

+

+## 验证FPGA 移植linux

+

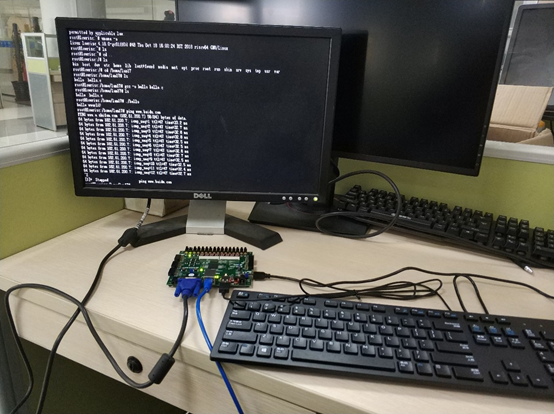

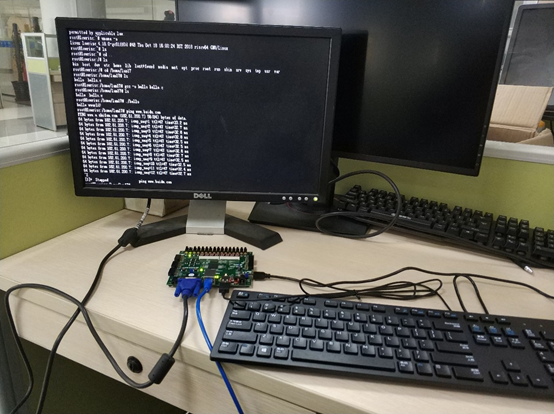

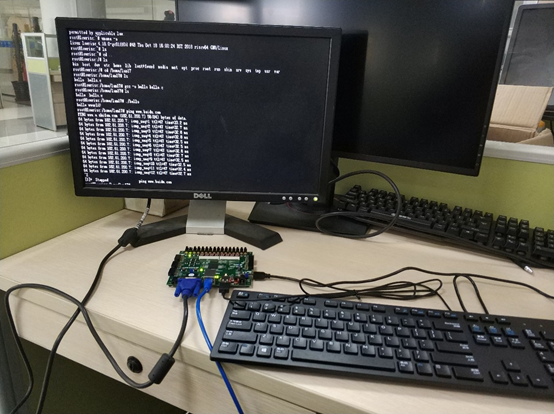

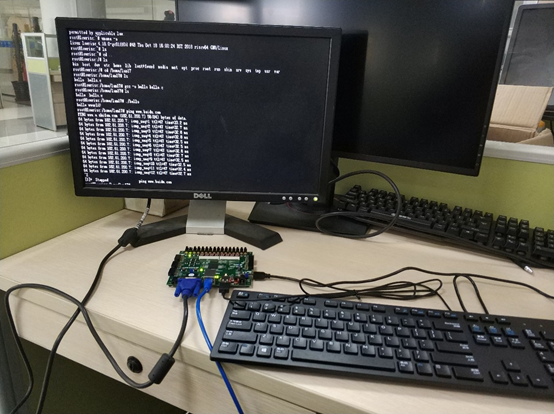

+通过 lowRISC 开源项目,基于 rocket 修改的软核上运行完整的 linux。支持键盘、显示器、网卡等常见通用设备,验证了riscv软核运行linux操作系统的可行性,为XiUOS进一步支持riscv软核提供了试验基础。

+* 生成riscv软核比特流

+* 裁剪编译 linux

+* 生成伯克利 bootloader(bbl)

+* 将软核写入 flash

+* 将 bbl 和 linux 写入 microSD卡

+* JP1 位于 USB / SD 位置,JP2 位于 USB 位置,电源选择 JP3位,usb底部的开关打开DIP-SW 1,引导linux从sd卡启动

+

+

+  +

+

+ 在Nexys A7-100T上基于riscv软核运行Linux

+

+

+```bash

+Debian GUN/Linux buster/sid lowrisc tty1

+lowrisc login: xiuos

+Password:

+Last login:Thu Jan 1 01:09:48 BST 1970 on tty1

+Linux lowrisc 4.18.0-gc81ff0d #48 Thu Oct 18 16:00:24 BST 2018 riscv64

+

+The programs included with the Debian GUN/linux system are free software;

+the exact distribution terms for each program are described in the

+individual files in /usr/share/doc/*/copyright.

+

+Debian GUN/linux comes with ABSOLUTELY NO WARRANT, to the extent

+permitted by applicable law.

+xiuos@lowrisc:~$ cat /proc/cpuinfo

+hart : 0

+isa : rv64imafdc

+mmu : sv39

+uarch : sifive,rocket0

+

+xiuos@lowrisc:~$ uname -a

+Linux lowrisc 4.18.0-gc81ff0d #48 Thu Oct 18 16:00:24 BST 2018 riscv64 GUN/linux

+xiuos@lowrisc:~$

+```

\ No newline at end of file

diff --git a/docs/doc/processor/riscv_sfcore.md b/docs/doc/processor/riscv_sfcore.md

index 311506b..7436af1 100644

--- a/docs/doc/processor/riscv_sfcore.md

+++ b/docs/doc/processor/riscv_sfcore.md

@@ -10,92 +10,26 @@ IP核的提供方式通常分为软核、固核和硬核这3类。软核(Soft IP

## 一些常见软核

### 开源RISCV软核

-1. Rocket,UC Berkeley 发起 RISC-V 项目的团队所设计的兼容 RISC-V 指令集的CPU核。为了设计一个新的指令集,UC Berkeley开发的一门“硬件构建语言”-Chisel。从功能上的角度来看,Chisel 可以将用户描述的硬件(写的代码)转化为等价的可综合的 Verilog HDL 代码或时等价的 C++ 仿真模型。

+1. Rocket,是 UC Berkeley 的 RISC-V 项目团队发起并设计的兼容 RISC-V 指令集的 CPU 核。它是一款64位、5级流水线、单发射顺序执行处理器,支持 MMU,支持分页虚拟内存,具有兼容 IEEE 754-2008 标准的 FPU,具有分支预测功能,具有 BTB(Branch Prediction Buff)、BHT(Branch History Table)、RAS(Return Address Stack),Rocket是采用 Chisel(Constructing Hardware in an Scala Embedded Language)编写硬件电路,可以通过编译得到对应的 Verilog 设计,还可以得到对应的 C++ 模拟器。

-2. PULPino, PULPino 是一个开源的微型控制系统,基于一个32位RISC-V核心,由瑞士苏黎世联邦理工学院开发。核心IPC接近1,完全支持基整数指令集(RV32I),压缩指令(RV32C)和部分支持乘法指令集扩展(RV32M)。

+2. PULPino, 是一个开源的微型控制系统,基于一个32位RISC-V核心,由瑞士苏黎世联邦理工学院开发。核心IPC接近1,完全支持基整数指令集 (RV32I),压缩指令 (RV32C) 和部分支持乘法指令集扩展 (RV32M)。

-3. Shakti,印度理工学院的一个项目,由 Verilog 编写,其中使用了大量第三方IP,根据需要分成了不同的类。该计划不仅构建开源,生产级处理器,还包括互连结构,验证工具,存储控制器,外围IP和SOC工具等相关组件。

+3. Shakti,印度理工学院的一个项目,由 Verilog 编写,其使用了大量第三方 IP,根据需要分成了不同的类。该计划不仅构建开源,生产级处理器,还包括互连结构,验证工具,存储控制器,外围 IP 和 SOC 工具等相关组件。

-4. 蜂鸟,国内最早比较成熟的 RISC-V 实现,由胡振波(现在芯来创始人)开发,使用Verilog设计,其开源CPU为E200,使用2级流水线。

+4. 蜂鸟,国内最早比较成熟的 RISC-V 实现,由胡振波(现在芯来创始人)开发,使用Verilog设计。其开源CPU为E200:使用2级流水线。

-5. tinyriscv,国内开发者在GitHub上开源的一个微 RISC-V 处理器核,用verilog语言编写,以最简单、最通俗易懂的方式实现RISC-V指令的功能,没有对代码做任何的优化。

+5. tinyriscv,国内开发者在GitHub上开源的一个微RISC-V处理器核,用verilog语言编写,以最简单、最通俗易懂的方式实现RISC-V指令的功能,没有对代码做任何的优化。

### 商业非开源软核

-1. MicroBlaze,RISC 微处理器, Xilinx 嵌入式产品系列的重要组件。MicroBlaze 是功能齐全的、更少指令集的 FPGA 优化型 32 位计算机 (RISC) 软处理器,可充分满足各种应用需求。作为一款高度可配置的易用型处理器,MicroBlaze 可在 FPGA 以及全可编程 (AP) SoC 产品系列中使用。它免费配套提供 Vivado 设计与系统版以及 Vivado Webpack 版。

+1. MicroBlaze,MicroBlaze 是功能齐全的、更少指令集的 FPGA 优化型 32 位 RISC 软处理器,可充分满足各种应用需求。MicroBlaze 是一款高度可配置的易用型处理器,可在 FPGA 以及全可编程 (AP) SoC 产品系列中使用。它免费配套提供 Vivado 设计与系统版以及 Vivado Webpack 版。

-2. Nios II系列,RSIC微理器,Altera 推出的32位RISC嵌入式处理器 。Nios II是应用于Intel FPGA的嵌入式软核处理器,它是Qsys嵌入式系统的核心部件,具

-有较强的性能和可定制特性。一片FPGA内部可以构建多个 Nios II 处理器,它们可以作为主CPU,也可以是协处理器,在同一芯片内部协调有序地完成整个复杂系统的各项功能。Nios II处理器内核是32位RISC架构(精简指令集架构)处理器,它包含了大多数现代32位处理器中常见的基本架构元素。

-

-## Nexys A7-100T设备参数

-Nexys A7-100T 是 Digilent 多孔 RAM-based Nexys 开发板的简易替代品。搭载Xilinx®Artix™-7 FPGA芯片,Nexys 4 DDR 是一个打开即用型的数字电路开发平台,帮助使用者能够在课堂环境下实现诸多工业领域的应用,配有高容量的大型FPGA芯片(Xilinx产品编号XC7A100T-1CSG324C)并集成了USB,以太网和其它端口。Nexys 4 DDR开发板能实现从理论型组合电路到强大的嵌入式处理器的多种设计。

-

-

-

-  -

-

- Nexys A7

-

-

-| 序号 | 描述 | 序号 | 描述 |

-| ---- | ---- | ---- | ---- |

-| 1 | 选择供电跳线 |13|CPU复位按键(用于软核)|

-| 2 | UART/JTAG共用USB接口 |14|FPGA 配置复位按键|

-| 3 | 外部配置跳线柱(SD/USB) |15|模拟信号Pmod端口(XADC)|

-| 4 | Pmod端口 |16|编程模式跳线柱|

-| 5 | 扩音器 |17|音频连接口|

-| 6 | 电源测试点 |18|VGA连接口|

-| 7 | 16个LED |19|FPGA编程完成LED|

-| 8 | 16个按键开关 |20|以太网连接口|

-| 9 | 8位7段数码管 |21|USB连接口|

-| 10 | 可选用与外部接线的JTAG端口 |22|(工业用)PIC24编程端口|

-| 11 | 5个按键开关 |23|电源开关|

-| 12 | 板载温度传感器 |24|电源接口|

+2. Nios II系列,是 Altera 推出的32位RISC嵌入式处理器。Nios II是应用于 Intel FPGA 的嵌入式软核处理器,它是 Qsys 嵌入式系统的核心部件,具有较强的性能和可定制特性。一片 FPGA 内部可以构建多个 Nios II 处理器,它们可以作为主 CPU,也可以是协处理器,在同一芯片内部协调有序地完成整个复杂系统的各项功能。Nios II 处理器内核是32位 RISC 架构处理器,包含了大多数现代32位处理器中常见的基本架构元素。

-### 验证FPGA 移植linux

-通过 lowRISC 开源项目,基于 rocket 修改的软核上运行完整的 linux。支持键盘、显示器、网卡等常见通用设备,验证了riscv软核运行linux操作系统的可行性,为XiUOS进一步支持riscv软核提供了试验基础。

-* 生成riscv软核比特流

-* 裁剪编译 linux

-* 生成伯克利 bootloader(bbl)

-* 将软核写入 flash

-* 将 bbl 和 linux 写入 microSD卡

-* JP1 位于 USB / SD 位置,JP2 位于 USB 位置,电源选择 JP3位,usb底部的开关打开DIP-SW 1,引导linux从sd卡启动

-

-  -

-

- 在Nexys A7-100T上基于riscv软核运行Linux

-

-```bash

-Debian GUN/Linux buster/sid lowrisc tty1

-lowrisc login: xiuos

-Password:

-Last login:Thu Jan 1 01:09:48 BST 1970 on tty1

-Linux lowrisc 4.18.0-gc81ff0d #48 Thu Oct 18 16:00:24 BST 2018 riscv64

-The programs included with the Debian GUN/linux system are free software;

-the exact distribution terms for each program are described in the

-individual files in /usr/share/doc/*/copyright.

-Debian GUN/linux comes with ABSOLUTELY NO WARRANT, to the extent

-permitted by applicable law.

-xiuos@lowrisc:~$ cat /proc/cpuinfo

-hart : 0

-isa : rv64imafdc

-mmu : sv39

-uarch : sifive,rocket0

-

-xiuos@lowrisc:~$ uname -a

-Linux lowrisc 4.18.0-gc81ff0d #48 Thu Oct 18 16:00:24 BST 2018 riscv64 GUN/linux

-xiuos@lowrisc:~$

-```

\ No newline at end of file

diff --git a/docs/doc/selfterminal/aiit-arm.md b/docs/doc/selfterminal/aiit-arm.md

index bed00d8..315e8cb 100644

--- a/docs/doc/selfterminal/aiit-arm.md

+++ b/docs/doc/selfterminal/aiit-arm.md

@@ -16,7 +16,7 @@ AIIT ARM-board是基于STM32F407ZGT6设计的一款低功耗智能物联网终

AIIT ARM-board拥有的资源包括:

* 集成在芯片内部的 FPU 和 DSP 指令集

-* 存储大小: 192KB SRAM、 512K FLASH

+* 存储大小: 192KB + 1 MB SRAM、 512K FLASH

* 摄像头接口: 1个

* 定时器:12 个 16 位定时器、 2 个 32 位高级定时器

* IIC硬件控制器: 3 个

+

+  +

+  +

+  -

-  -

-