forked from xuos/xiuos

Merge branch 'prepare_for_master' of https://git.trustie.net/xuos/xiuos into wgz

This commit is contained in:

339

Ubiquitous/RT_Thread/aiit_board/xidatong/.config

Normal file

339

Ubiquitous/RT_Thread/aiit_board/xidatong/.config

Normal file

@@ -0,0 +1,339 @@

|

||||

#

|

||||

# Automatically generated file; DO NOT EDIT.

|

||||

# RT-Thread Configuration

|

||||

#

|

||||

CONFIG_ROOT_DIR="../../../.."

|

||||

CONFIG_BSP_DIR="."

|

||||

CONFIG_RT_Thread_DIR="../.."

|

||||

CONFIG_RTT_DIR="../../rt-thread"

|

||||

|

||||

#

|

||||

# RT-Thread Kernel

|

||||

#

|

||||

CONFIG_RT_NAME_MAX=8

|

||||

# CONFIG_RT_USING_BIG_ENDIAN is not set

|

||||

# CONFIG_RT_USING_ARCH_DATA_TYPE is not set

|

||||

# CONFIG_RT_USING_SMP is not set

|

||||

CONFIG_RT_ALIGN_SIZE=4

|

||||

# CONFIG_RT_THREAD_PRIORITY_8 is not set

|

||||

CONFIG_RT_THREAD_PRIORITY_32=y

|

||||

# CONFIG_RT_THREAD_PRIORITY_256 is not set

|

||||

CONFIG_RT_THREAD_PRIORITY_MAX=32

|

||||

CONFIG_RT_TICK_PER_SECOND=100

|

||||

CONFIG_RT_USING_OVERFLOW_CHECK=y

|

||||

CONFIG_RT_USING_HOOK=y

|

||||

CONFIG_RT_USING_IDLE_HOOK=y

|

||||

CONFIG_RT_IDLE_HOOK_LIST_SIZE=4

|

||||

CONFIG_IDLE_THREAD_STACK_SIZE=256

|

||||

# CONFIG_RT_USING_TIMER_SOFT is not set

|

||||

|

||||

#

|

||||

# kservice optimization

|

||||

#

|

||||

CONFIG_RT_KSERVICE_USING_STDLIB=y

|

||||

# CONFIG_RT_KSERVICE_USING_TINY_SIZE is not set

|

||||

# CONFIG_RT_USING_ASM_MEMCPY is not set

|

||||

CONFIG_RT_DEBUG=y

|

||||

CONFIG_RT_DEBUG_COLOR=y

|

||||

# CONFIG_RT_DEBUG_INIT_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_THREAD_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_SCHEDULER_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_IPC_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_TIMER_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_IRQ_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_MEM_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_SLAB_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_MEMHEAP_CONFIG is not set

|

||||

# CONFIG_RT_DEBUG_MODULE_CONFIG is not set

|

||||

|

||||

#

|

||||

# Inter-Thread communication

|

||||

#

|

||||

CONFIG_RT_USING_SEMAPHORE=y

|

||||

CONFIG_RT_USING_MUTEX=y

|

||||

CONFIG_RT_USING_EVENT=y

|

||||

CONFIG_RT_USING_MAILBOX=y

|

||||

CONFIG_RT_USING_MESSAGEQUEUE=y

|

||||

# CONFIG_RT_USING_SIGNALS is not set

|

||||

|

||||

#

|

||||

# Memory Management

|

||||

#

|

||||

CONFIG_RT_USING_MEMPOOL=y

|

||||

CONFIG_RT_USING_MEMHEAP=y

|

||||

CONFIG_RT_USING_MEMHEAP_AUTO_BINDING=y

|

||||

# CONFIG_RT_USING_NOHEAP is not set

|

||||

# CONFIG_RT_USING_SMALL_MEM is not set

|

||||

# CONFIG_RT_USING_SLAB is not set

|

||||

CONFIG_RT_USING_MEMHEAP_AS_HEAP=y

|

||||

# CONFIG_RT_USING_USERHEAP is not set

|

||||

# CONFIG_RT_USING_MEMTRACE is not set

|

||||

CONFIG_RT_USING_HEAP=y

|

||||

|

||||

#

|

||||

# Kernel Device Object

|

||||

#

|

||||

CONFIG_RT_USING_DEVICE=y

|

||||

# CONFIG_RT_USING_DEVICE_OPS is not set

|

||||

# CONFIG_RT_USING_INTERRUPT_INFO is not set

|

||||

CONFIG_RT_USING_CONSOLE=y

|

||||

CONFIG_RT_CONSOLEBUF_SIZE=128

|

||||

CONFIG_RT_CONSOLE_DEVICE_NAME="uart1"

|

||||

# CONFIG_RT_PRINTF_LONGLONG is not set

|

||||

CONFIG_RT_VER_NUM=0x40004

|

||||

# CONFIG_RT_USING_CPU_FFS is not set

|

||||

# CONFIG_ARCH_CPU_STACK_GROWS_UPWARD is not set

|

||||

|

||||

#

|

||||

# RT-Thread Components

|

||||

#

|

||||

CONFIG_RT_USING_COMPONENTS_INIT=y

|

||||

CONFIG_RT_USING_USER_MAIN=y

|

||||

CONFIG_RT_MAIN_THREAD_STACK_SIZE=2048

|

||||

CONFIG_RT_MAIN_THREAD_PRIORITY=10

|

||||

|

||||

#

|

||||

# C++ features

|

||||

#

|

||||

# CONFIG_RT_USING_CPLUSPLUS is not set

|

||||

|

||||

#

|

||||

# Command shell

|

||||

#

|

||||

CONFIG_RT_USING_FINSH=y

|

||||

CONFIG_RT_USING_MSH=y

|

||||

CONFIG_FINSH_USING_MSH=y

|

||||

CONFIG_FINSH_THREAD_NAME="tshell"

|

||||

CONFIG_FINSH_THREAD_PRIORITY=20

|

||||

CONFIG_FINSH_THREAD_STACK_SIZE=4096

|

||||

CONFIG_FINSH_USING_HISTORY=y

|

||||

CONFIG_FINSH_HISTORY_LINES=5

|

||||

CONFIG_FINSH_USING_SYMTAB=y

|

||||

CONFIG_FINSH_CMD_SIZE=80

|

||||

CONFIG_MSH_USING_BUILT_IN_COMMANDS=y

|

||||

CONFIG_FINSH_USING_DESCRIPTION=y

|

||||

# CONFIG_FINSH_ECHO_DISABLE_DEFAULT is not set

|

||||

# CONFIG_FINSH_USING_AUTH is not set

|

||||

CONFIG_FINSH_ARG_MAX=10

|

||||

|

||||

#

|

||||

# Device virtual file system

|

||||

#

|

||||

CONFIG_RT_USING_DFS=y

|

||||

CONFIG_DFS_USING_WORKDIR=y

|

||||

CONFIG_DFS_FILESYSTEMS_MAX=4

|

||||

CONFIG_DFS_FILESYSTEM_TYPES_MAX=4

|

||||

CONFIG_DFS_FD_MAX=16

|

||||

# CONFIG_RT_USING_DFS_MNTTABLE is not set

|

||||

# CONFIG_RT_USING_DFS_ELMFAT is not set

|

||||

CONFIG_RT_USING_DFS_DEVFS=y

|

||||

# CONFIG_RT_USING_DFS_ROMFS is not set

|

||||

# CONFIG_RT_USING_DFS_RAMFS is not set

|

||||

|

||||

#

|

||||

# Device Drivers

|

||||

#

|

||||

CONFIG_RT_USING_DEVICE_IPC=y

|

||||

CONFIG_RT_PIPE_BUFSZ=512

|

||||

# CONFIG_RT_USING_SYSTEM_WORKQUEUE is not set

|

||||

CONFIG_RT_USING_SERIAL=y

|

||||

CONFIG_RT_USING_SERIAL_V1=y

|

||||

# CONFIG_RT_USING_SERIAL_V2 is not set

|

||||

CONFIG_RT_SERIAL_USING_DMA=y

|

||||

CONFIG_RT_SERIAL_RB_BUFSZ=64

|

||||

# CONFIG_RT_USING_CAN is not set

|

||||

# CONFIG_RT_USING_HWTIMER is not set

|

||||

CONFIG_RT_USING_CPUTIME=y

|

||||

# CONFIG_RT_USING_I2C is not set

|

||||

# CONFIG_RT_USING_PHY is not set

|

||||

CONFIG_RT_USING_PIN=y

|

||||

# CONFIG_RT_USING_ADC is not set

|

||||

# CONFIG_RT_USING_DAC is not set

|

||||

# CONFIG_RT_USING_PWM is not set

|

||||

# CONFIG_RT_USING_MTD_NOR is not set

|

||||

# CONFIG_RT_USING_MTD_NAND is not set

|

||||

# CONFIG_RT_USING_PM is not set

|

||||

# CONFIG_RT_USING_RTC is not set

|

||||

# CONFIG_RT_USING_SDIO is not set

|

||||

# CONFIG_RT_USING_SPI is not set

|

||||

# CONFIG_RT_USING_WDT is not set

|

||||

# CONFIG_RT_USING_AUDIO is not set

|

||||

# CONFIG_RT_USING_SENSOR is not set

|

||||

# CONFIG_RT_USING_TOUCH is not set

|

||||

# CONFIG_RT_USING_HWCRYPTO is not set

|

||||

# CONFIG_RT_USING_PULSE_ENCODER is not set

|

||||

# CONFIG_RT_USING_INPUT_CAPTURE is not set

|

||||

# CONFIG_RT_USING_WIFI is not set

|

||||

|

||||

#

|

||||

# Using USB

|

||||

#

|

||||

# CONFIG_RT_USING_USB_HOST is not set

|

||||

# CONFIG_RT_USING_USB_DEVICE is not set

|

||||

|

||||

#

|

||||

# POSIX layer and C standard library

|

||||

#

|

||||

CONFIG_RT_USING_LIBC=y

|

||||

CONFIG_RT_USING_PTHREADS=y

|

||||

CONFIG_PTHREAD_NUM_MAX=8

|

||||

CONFIG_RT_USING_POSIX=y

|

||||

# CONFIG_RT_USING_POSIX_MMAP is not set

|

||||

# CONFIG_RT_USING_POSIX_TERMIOS is not set

|

||||

# CONFIG_RT_USING_POSIX_GETLINE is not set

|

||||

# CONFIG_RT_USING_POSIX_AIO is not set

|

||||

CONFIG_RT_LIBC_USING_TIME=y

|

||||

# CONFIG_RT_USING_MODULE is not set

|

||||

CONFIG_RT_LIBC_DEFAULT_TIMEZONE=8

|

||||

|

||||

#

|

||||

# Network

|

||||

#

|

||||

|

||||

#

|

||||

# Socket abstraction layer

|

||||

#

|

||||

# CONFIG_RT_USING_SAL is not set

|

||||

|

||||

#

|

||||

# Network interface device

|

||||

#

|

||||

# CONFIG_RT_USING_NETDEV is not set

|

||||

|

||||

#

|

||||

# light weight TCP/IP stack

|

||||

#

|

||||

# CONFIG_RT_USING_LWIP is not set

|

||||

|

||||

#

|

||||

# AT commands

|

||||

#

|

||||

# CONFIG_RT_USING_AT is not set

|

||||

|

||||

#

|

||||

# VBUS(Virtual Software BUS)

|

||||

#

|

||||

# CONFIG_RT_USING_VBUS is not set

|

||||

|

||||

#

|

||||

# Utilities

|

||||

#

|

||||

# CONFIG_RT_USING_RYM is not set

|

||||

# CONFIG_RT_USING_ULOG is not set

|

||||

# CONFIG_RT_USING_UTEST is not set

|

||||

# CONFIG_RT_USING_VAR_EXPORT is not set

|

||||

# CONFIG_RT_USING_RT_LINK is not set

|

||||

|

||||

#

|

||||

# RT-Thread Utestcases

|

||||

#

|

||||

# CONFIG_RT_USING_UTESTCASES is not set

|

||||

|

||||

#

|

||||

# Hardware Drivers Config

|

||||

#

|

||||

CONFIG_SOC_IMXRT1052CVL5B=y

|

||||

|

||||

#

|

||||

# On-chip Peripheral Drivers

|

||||

#

|

||||

CONFIG_BSP_USING_BOOT_IMAGE=y

|

||||

# CONFIG_BSP_USING_DMA is not set

|

||||

CONFIG_BSP_USING_GPIO=y

|

||||

CONFIG_BSP_USING_LPUART=y

|

||||

CONFIG_BSP_USING_LPUART1=y

|

||||

# CONFIG_BSP_LPUART1_RX_USING_DMA is not set

|

||||

# CONFIG_BSP_LPUART1_TX_USING_DMA is not set

|

||||

# CONFIG_BSP_USING_LPUART2 is not set

|

||||

# CONFIG_BSP_USING_LPUART3 is not set

|

||||

# CONFIG_BSP_USING_LPUART4 is not set

|

||||

# CONFIG_BSP_USING_LPUART8 is not set

|

||||

# CONFIG_BSP_USING_I2C is not set

|

||||

# CONFIG_BSP_USING_CAN is not set

|

||||

# CONFIG_BSP_USING_RTC is not set

|

||||

|

||||

#

|

||||

# Onboard Peripheral Drivers

|

||||

#

|

||||

CONFIG_BSP_USING_SDRAM=y

|

||||

|

||||

#

|

||||

# MicroPython

|

||||

#

|

||||

# CONFIG_PKG_USING_MICROPYTHON is not set

|

||||

|

||||

#

|

||||

# More Drivers

|

||||

#

|

||||

# CONFIG_PKG_USING_RW007 is not set

|

||||

# CONFIG_DRV_USING_OV2640 is not set

|

||||

|

||||

#

|

||||

# APP_Framework

|

||||

#

|

||||

|

||||

#

|

||||

# Framework

|

||||

#

|

||||

CONFIG_TRANSFORM_LAYER_ATTRIUBUTE=y

|

||||

# CONFIG_ADD_XIZI_FETURES is not set

|

||||

# CONFIG_ADD_NUTTX_FETURES is not set

|

||||

CONFIG_ADD_RTTHREAD_FETURES=y

|

||||

# CONFIG_SUPPORT_SENSOR_FRAMEWORK is not set

|

||||

# CONFIG_SUPPORT_CONNECTION_FRAMEWORK is not set

|

||||

# CONFIG_SUPPORT_KNOWING_FRAMEWORK is not set

|

||||

# CONFIG_SUPPORT_CONTROL_FRAMEWORK is not set

|

||||

|

||||

#

|

||||

# Security

|

||||

#

|

||||

# CONFIG_CRYPTO is not set

|

||||

|

||||

#

|

||||

# Applications

|

||||

#

|

||||

|

||||

#

|

||||

# config stack size and priority of main task

|

||||

#

|

||||

CONFIG_MAIN_KTASK_STACK_SIZE=1024

|

||||

|

||||

#

|

||||

# ota app

|

||||

#

|

||||

# CONFIG_APPLICATION_OTA is not set

|

||||

|

||||

#

|

||||

# test app

|

||||

#

|

||||

# CONFIG_USER_TEST is not set

|

||||

|

||||

#

|

||||

# connection app

|

||||

#

|

||||

# CONFIG_APPLICATION_CONNECTION is not set

|

||||

|

||||

#

|

||||

# control app

|

||||

#

|

||||

|

||||

#

|

||||

# knowing app

|

||||

#

|

||||

# CONFIG_APPLICATION_KNOWING is not set

|

||||

|

||||

#

|

||||

# sensor app

|

||||

#

|

||||

# CONFIG_APPLICATION_SENSOR is not set

|

||||

# CONFIG_USING_EMBEDDED_DATABASE_APP is not set

|

||||

|

||||

#

|

||||

# lib

|

||||

#

|

||||

CONFIG_APP_SELECT_NEWLIB=y

|

||||

# CONFIG_APP_SELECT_OTHER_LIB is not set

|

||||

# CONFIG_LIB_USING_CJSON is not set

|

||||

# CONFIG_LIB_USING_QUEUE is not set

|

||||

# CONFIG_LIB_LV is not set

|

||||

# CONFIG_USING_EMBEDDED_DATABASE is not set

|

||||

29

Ubiquitous/RT_Thread/aiit_board/xidatong/Kconfig

Normal file

29

Ubiquitous/RT_Thread/aiit_board/xidatong/Kconfig

Normal file

@@ -0,0 +1,29 @@

|

||||

mainmenu "RT-Thread Configuration"

|

||||

|

||||

config ROOT_DIR

|

||||

string

|

||||

default "../../../.."

|

||||

|

||||

config BSP_DIR

|

||||

string

|

||||

default "."

|

||||

|

||||

config RT_Thread_DIR

|

||||

string

|

||||

default "../.."

|

||||

|

||||

config RTT_DIR

|

||||

string

|

||||

default "../../rt-thread"

|

||||

|

||||

config APP_DIR

|

||||

string

|

||||

default "../../../../APP_Framework"

|

||||

|

||||

source "$RTT_DIR/Kconfig"

|

||||

source "$RTT_DIR/bsp/imxrt/libraries/Kconfig"

|

||||

source "board/Kconfig"

|

||||

source "$RT_Thread_DIR/micropython/Kconfig"

|

||||

source "$RT_Thread_DIR/app_match_rt-thread/Kconfig"

|

||||

source "$ROOT_DIR/APP_Framework/Kconfig"

|

||||

|

||||

121

Ubiquitous/RT_Thread/aiit_board/xidatong/README.md

Normal file

121

Ubiquitous/RT_Thread/aiit_board/xidatong/README.md

Normal file

@@ -0,0 +1,121 @@

|

||||

# XiDaTong_ARM_Reference_Resource

|

||||

|

||||

## 1. 矽达通介绍

|

||||

|

||||

矽达通外观图:

|

||||

|

||||

|

||||

|

||||

拆开后盖:

|

||||

|

||||

|

||||

|

||||

矽达通烧录这里介绍两种方式,分别是 NXP-MCUBootUtility 和 Keil MDK5

|

||||

|

||||

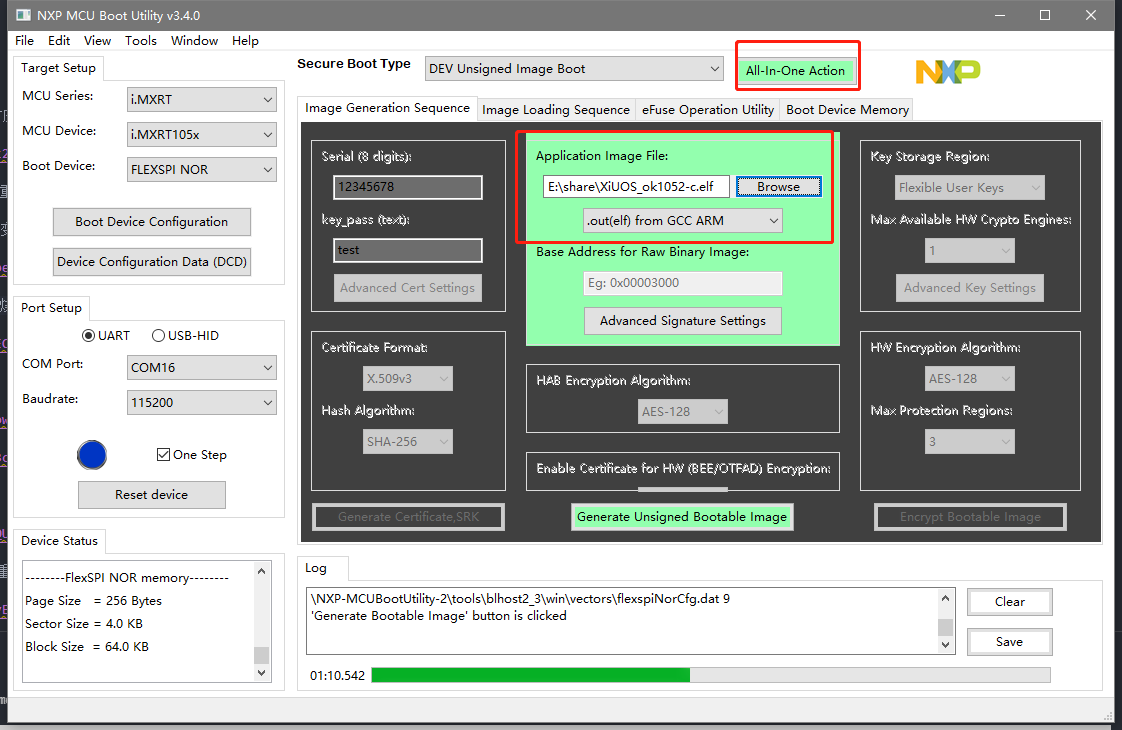

## 2. NXP-MCUBootUtility 方式烧录

|

||||

|

||||

**[NXP-MCUBootUtility](https://github.com/JayHeng/NXP-MCUBootUtility/tree/v3.4.0)** 是一款开源免费的专为 NXP MCU 安全启动而设计的 GUI 工具。目前主要支持 i.MXRT、LPC、Kinetis 系列 MCU 芯片

|

||||

|

||||

> ### 测试环境

|

||||

|

||||

- Windows

|

||||

|

||||

- NXP-MCUBootUtility v3.4.0

|

||||

|

||||

> ### 烧录流程

|

||||

|

||||

将矽达通串口1通过 usb 转串口连接至电脑,并在电脑端查看到相应端口,如下图,com15

|

||||

|

||||

|

||||

|

||||

打开 NXP-MCUBootUtility.exe

|

||||

|

||||

确保一下配置选项正确,COM Port记得选择上述对应的串口

|

||||

|

||||

|

||||

|

||||

将拨码开关拨到 1 on 2 on 3 off 4 off 进入 Serial Download Programming(SDP) 模式, 重新连接电源

|

||||

|

||||

先点击 Connect to ROM,若连接成功按钮会变蓝

|

||||

|

||||

|

||||

|

||||

在 Application Image File 一栏中选择要烧录的 elf 文件,文件格式选择 .out(elf) from GCC ARM,然后点击 All-In-One Action 烧录即可

|

||||

|

||||

|

||||

|

||||

烧录完后后,将拨码开关拨回 1 off 2 off 3 off 4 off 进入 nor-flash 启动模式,重新上电,即可从 QSPI Flash 启动程序,此时可以从串口看到调试信息

|

||||

|

||||

`注:由于采用串口烧录,在连接和烧录的时候记得先关闭串口调试工具`

|

||||

|

||||

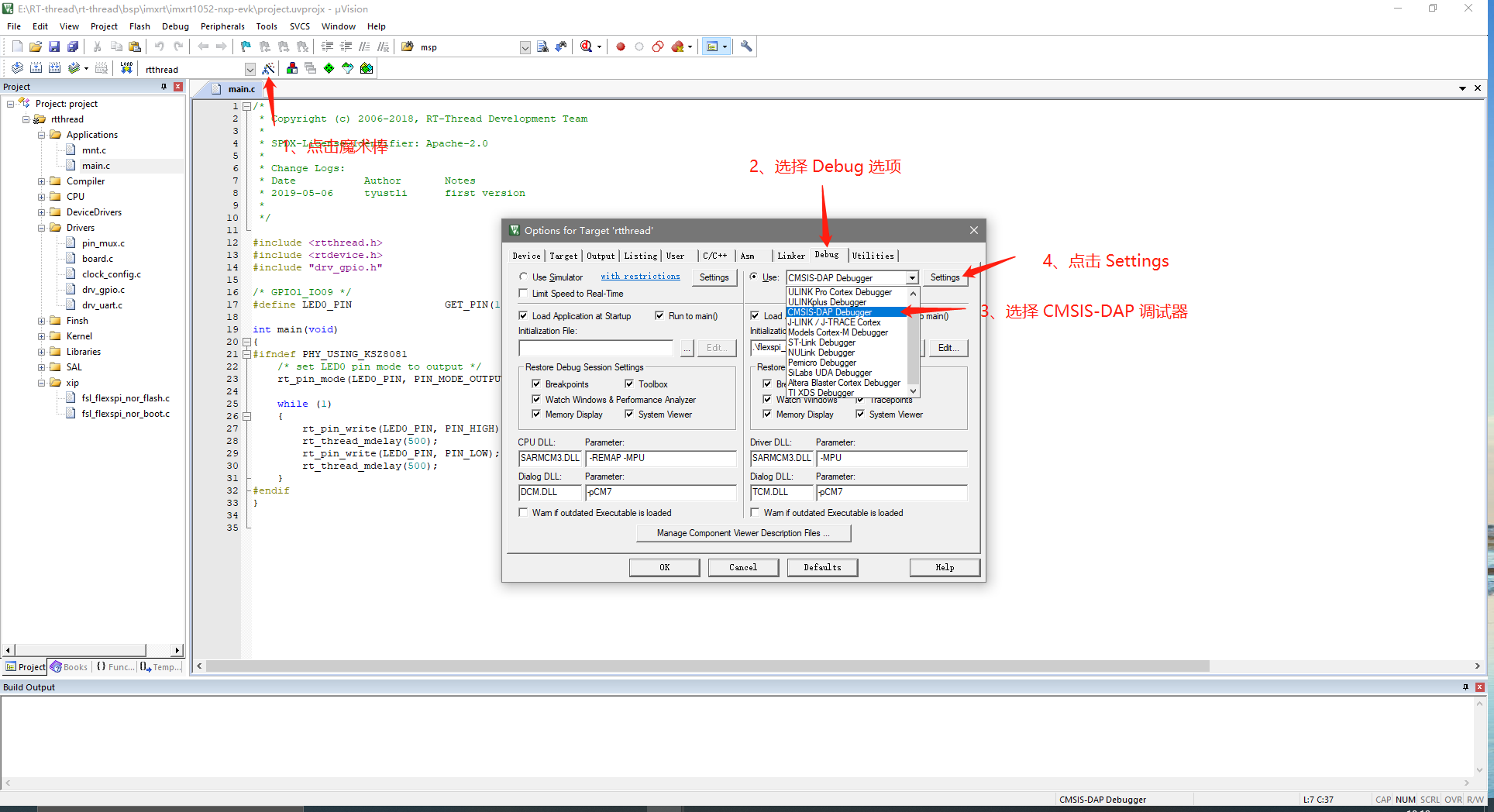

## 2. Keil MDK 方式烧录

|

||||

|

||||

Keil MDK 是一系列基于 Arm Cortex-M 的微控制器设备的完整软件开发环境,可以自行去官网 **[购买下载](https://www.keil.com/download/product/)** ,需要注意的是请选择使用 Keil MDK5.24a 及以上版本

|

||||

|

||||

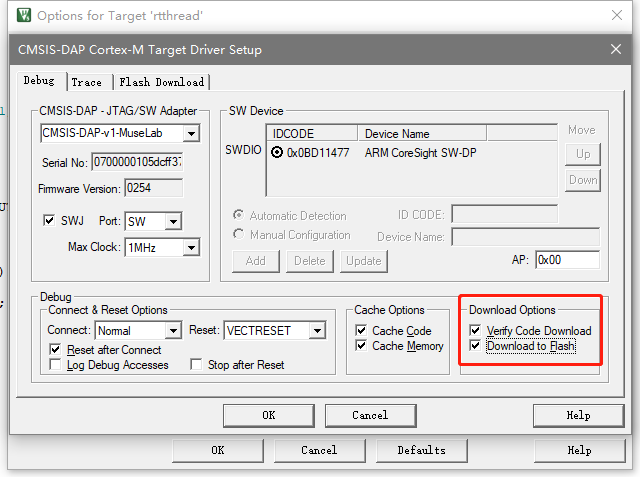

开发板连接 CMSIS-DAP 调试器,如下图所示,连接 DIO/CLK/GND 对应的三个引脚即可

|

||||

|

||||

|

||||

|

||||

> ### 芯片支持包导入

|

||||

|

||||

去keil官网 [http://www.keil.com/dd2/pack/#/eula-container](http://www.keil.com/dd2/pack/#/eula-container) 下载对应的板级安装包

|

||||

|

||||

|

||||

|

||||

注意: 安装包可能随时间推移,版本有所改动,可选择最新版本下载。

|

||||

|

||||

下载完成,安装即可。

|

||||

|

||||

> ### 烧写固件安装

|

||||

|

||||

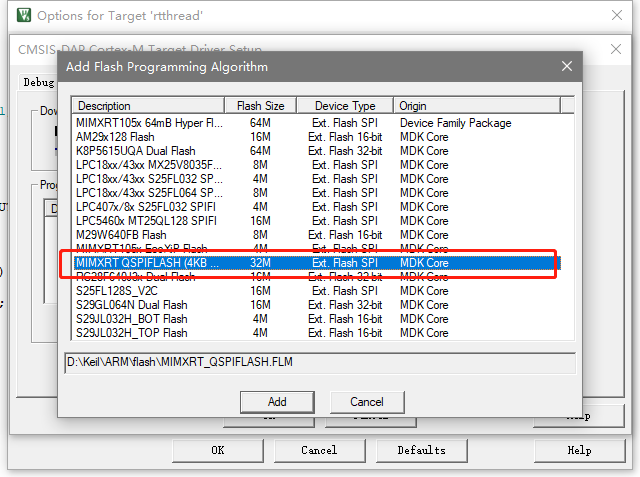

将开发板烧写固件复制到 Keil5 安装目录 Keil_v5\ARM\Flash\MIMXRT_QSPIFLASH.FLM,该固件可以兼容32M以下nor Flash烧写。

|

||||

|

||||

例如: c:\Keil_v5\ARM\Flash\MIMXRT_QSPIFLASH.FLM

|

||||

|

||||

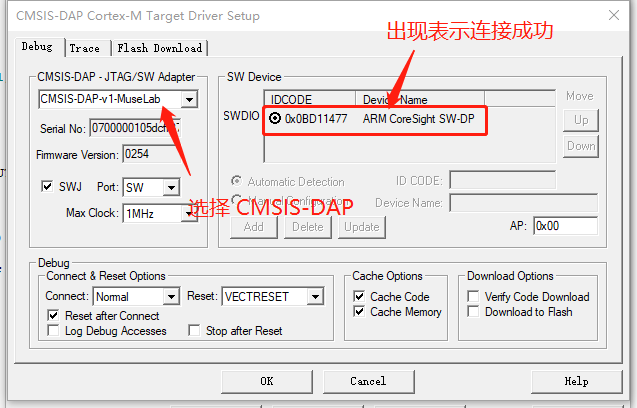

> ### Keil 环境配置

|

||||

|

||||

查看仿真器是否连接成功:

|

||||

|

||||

|

||||

|

||||

|

||||

|

||||

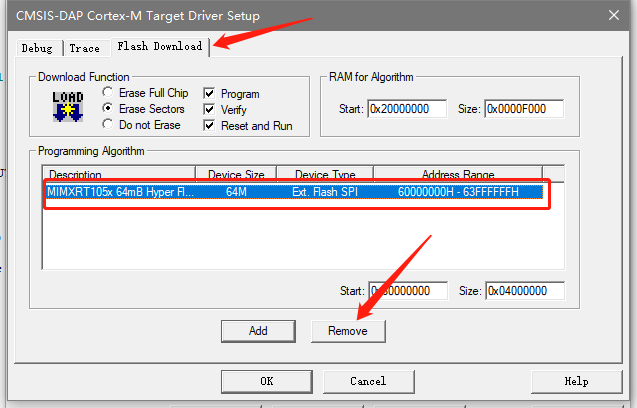

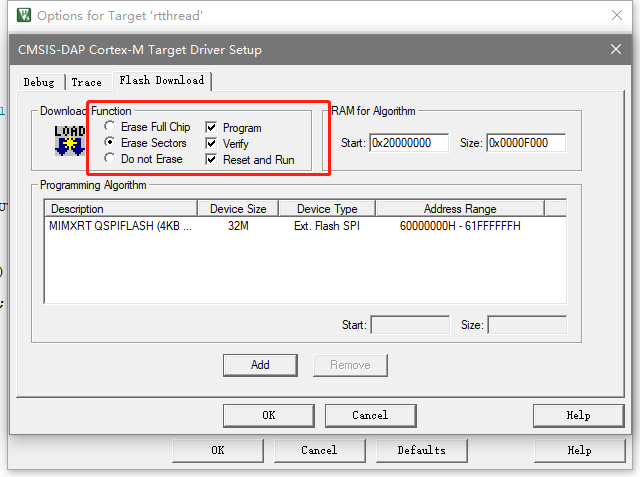

> ### 添加烧写固件

|

||||

|

||||

选择 Flash Download,删除原来的烧写配置

|

||||

|

||||

|

||||

|

||||

添加该烧写固件,size 大小为 32MB

|

||||

|

||||

|

||||

|

||||

下载的一些设置记得勾上:

|

||||

|

||||

|

||||

|

||||

然后编译烧录即可,keil下载不需要进入 SDP 模式,无需拨拨码开关。

|

||||

|

||||

|

||||

|

||||

## 3.矽达通硬件资源

|

||||

|

||||

| 端口 | 功能 |

|

||||

| :------------: | :----------------: |

|

||||

| uart1 | shell |

|

||||

| uart3 | 485CH1(外围接口) |

|

||||

| uart4 | 485CH2(外围接口) |

|

||||

| uart8 | ec200t 4G 通讯 |

|

||||

| uart2 | wifi esp07 |

|

||||

| ch438 EXTU2 | Bluetooth HC08 |

|

||||

| ch438 EXTU3 | Lora E220-400T22S |

|

||||

| ch438 EXTU1 | zigbee E18-MS1PA1 |

|

||||

| SD | sd卡 |

|

||||

| usb1 | ec200t 4G通讯 |

|

||||

| usb2 | 外围usb接口 |

|

||||

| can | can外围接口 |

|

||||

| IIC | 屏幕 |

|

||||

| 其他CH438 EXTU | 外围接口 |

|

||||

|

||||

|

||||

|

||||

14

Ubiquitous/RT_Thread/aiit_board/xidatong/SConscript

Normal file

14

Ubiquitous/RT_Thread/aiit_board/xidatong/SConscript

Normal file

@@ -0,0 +1,14 @@

|

||||

# for module compiling

|

||||

import os

|

||||

from building import *

|

||||

|

||||

cwd = GetCurrentDir()

|

||||

objs = []

|

||||

list = os.listdir(cwd)

|

||||

|

||||

for d in list:

|

||||

path = os.path.join(cwd, d)

|

||||

if os.path.isfile(os.path.join(path, 'SConscript')):

|

||||

objs = objs + SConscript(os.path.join(d, 'SConscript'))

|

||||

|

||||

Return('objs')

|

||||

85

Ubiquitous/RT_Thread/aiit_board/xidatong/SConstruct

Normal file

85

Ubiquitous/RT_Thread/aiit_board/xidatong/SConstruct

Normal file

@@ -0,0 +1,85 @@

|

||||

import os

|

||||

import sys

|

||||

import rtconfig

|

||||

|

||||

if os.getenv('RTT_ROOT'):

|

||||

RTT_ROOT = os.getenv('RTT_ROOT')

|

||||

else:

|

||||

RTT_ROOT = os.path.normpath(os.getcwd() + '/../../rt-thread')

|

||||

|

||||

sys.path = sys.path + [os.path.join(RTT_ROOT, 'tools')]

|

||||

try:

|

||||

from building import *

|

||||

except:

|

||||

print('Cannot found RT-Thread root directory, please check RTT_ROOT')

|

||||

print(RTT_ROOT)

|

||||

exit(-1)

|

||||

|

||||

TARGET = 'rtthread.' + rtconfig.TARGET_EXT

|

||||

DefaultEnvironment(tools=[])

|

||||

if rtconfig.PLATFORM == 'armcc':

|

||||

env = Environment(tools = ['mingw'],

|

||||

AS = rtconfig.AS, ASFLAGS = rtconfig.AFLAGS,

|

||||

CC = rtconfig.CC, CFLAGS = rtconfig.CFLAGS,

|

||||

CXX = rtconfig.CXX, CXXFLAGS = rtconfig.CXXFLAGS,

|

||||

AR = rtconfig.AR, ARFLAGS = '-rc',

|

||||

LINK = rtconfig.LINK, LINKFLAGS = rtconfig.LFLAGS,

|

||||

# overwrite cflags, because cflags has '--C99'

|

||||

CXXCOM = '$CXX -o $TARGET --cpp -c $CXXFLAGS $_CCCOMCOM $SOURCES')

|

||||

else:

|

||||

env = Environment(tools = ['mingw'],

|

||||

AS = rtconfig.AS, ASFLAGS = rtconfig.AFLAGS,

|

||||

CC = rtconfig.CC, CFLAGS = rtconfig.CFLAGS,

|

||||

CXX = rtconfig.CXX, CXXFLAGS = rtconfig.CXXFLAGS,

|

||||

AR = rtconfig.AR, ARFLAGS = '-rc',

|

||||

LINK = rtconfig.LINK, LINKFLAGS = rtconfig.LFLAGS,

|

||||

CXXCOM = '$CXX -o $TARGET -c $CXXFLAGS $_CCCOMCOM $SOURCES')

|

||||

|

||||

env.PrependENVPath('PATH', rtconfig.EXEC_PATH)

|

||||

|

||||

if rtconfig.PLATFORM == 'iar':

|

||||

env.Replace(CCCOM = ['$CC $CFLAGS $CPPFLAGS $_CPPDEFFLAGS $_CPPINCFLAGS -o $TARGET $SOURCES'])

|

||||

env.Replace(ARFLAGS = [''])

|

||||

env.Replace(LINKCOM = env["LINKCOM"] + ' --map rtthread.map')

|

||||

|

||||

Export('RTT_ROOT')

|

||||

Export('rtconfig')

|

||||

|

||||

SDK_ROOT = os.path.abspath('./')

|

||||

|

||||

#if os.path.exists(SDK_ROOT + '/libraries'):

|

||||

# libraries_path_prefix = SDK_ROOT + '/libraries'

|

||||

#else:

|

||||

# libraries_path_prefix = os.path.dirname(SDK_ROOT) + '/libraries'

|

||||

libraries_path_prefix = RTT_ROOT + '/bsp/imxrt/libraries'

|

||||

SDK_LIB = libraries_path_prefix

|

||||

Export('SDK_LIB')

|

||||

|

||||

# prepare building environment

|

||||

objs = PrepareBuilding(env, RTT_ROOT, has_libcpu=False)

|

||||

|

||||

imxrt_library = 'MIMXRT1050'

|

||||

rtconfig.BSP_LIBRARY_TYPE = imxrt_library

|

||||

|

||||

# include libraries

|

||||

objs.extend(SConscript(os.path.join(libraries_path_prefix, imxrt_library, 'SConscript')))

|

||||

|

||||

# include drivers

|

||||

objs.extend(SConscript(os.path.join(libraries_path_prefix, 'drivers', 'SConscript')))

|

||||

|

||||

# include more drivers

|

||||

objs.extend(SConscript(os.getcwd() + '/../../app_match_rt-thread/SConscript'))

|

||||

|

||||

# include APP_Framework/Framework

|

||||

objs.extend(SConscript(os.getcwd() + '/../../../../APP_Framework/Framework/SConscript'))

|

||||

|

||||

# include APP_Framework/Applications

|

||||

objs.extend(SConscript(os.getcwd() + '/../../../../APP_Framework/Applications/SConscript'))

|

||||

|

||||

# include APP_Framework/lib

|

||||

objs.extend(SConscript(os.getcwd() + '/../../../../APP_Framework/lib/SConscript'))

|

||||

|

||||

# include Ubiquitous/RT-Thread/micropython

|

||||

objs.extend(SConscript(os.getcwd() + '/../../micropython/SConscript'))

|

||||

# make a building

|

||||

DoBuilding(TARGET, objs)

|

||||

@@ -0,0 +1,17 @@

|

||||

import os

|

||||

import rtconfig

|

||||

from building import *

|

||||

|

||||

cwd = GetCurrentDir()

|

||||

src = Glob('*.c')

|

||||

CPPPATH = [cwd]

|

||||

|

||||

# add for startup script

|

||||

if rtconfig.CROSS_TOOL == 'gcc':

|

||||

CPPDEFINES = ['__START=entry']

|

||||

else:

|

||||

CPPDEFINES = []

|

||||

|

||||

group = DefineGroup('Applications', src, depend = [''], CPPPATH = CPPPATH, CPPDEFINES=CPPDEFINES)

|

||||

|

||||

Return('group')

|

||||

50

Ubiquitous/RT_Thread/aiit_board/xidatong/applications/main.c

Normal file

50

Ubiquitous/RT_Thread/aiit_board/xidatong/applications/main.c

Normal file

@@ -0,0 +1,50 @@

|

||||

/*

|

||||

* Copyright (c) 2006-2018, RT-Thread Development Team

|

||||

*

|

||||

* SPDX-License-Identifier: Apache-2.0

|

||||

*

|

||||

* Change Logs:

|

||||

* Date Author Notes

|

||||

* 2019-04-29 tyustli first version

|

||||

*

|

||||

*/

|

||||

|

||||

#include <rtdevice.h>

|

||||

#include <rtthread.h>

|

||||

#include "drv_gpio.h"

|

||||

#include <board.h>

|

||||

|

||||

/* defined the LED pin: GPIO1_IO9 */

|

||||

#define LED0_PIN GET_PIN(1,9)

|

||||

|

||||

int main(void)

|

||||

{

|

||||

/* set LED0 pin mode to output */

|

||||

rt_pin_mode(LED0_PIN, PIN_MODE_OUTPUT);

|

||||

rt_kprintf("XIUOS xidatong build %s %s\n",__DATE__,__TIME__);

|

||||

while (1)

|

||||

{

|

||||

rt_pin_write(LED0_PIN, PIN_HIGH);

|

||||

rt_thread_mdelay(500);

|

||||

rt_pin_write(LED0_PIN, PIN_LOW);

|

||||

rt_thread_mdelay(500);

|

||||

}

|

||||

}

|

||||

|

||||

#ifdef BSP_USING_SDRAM

|

||||

static void sram_test2(void)

|

||||

{

|

||||

char *p =NULL;

|

||||

p = rt_malloc(1024*1024*8);

|

||||

if(p == NULL)

|

||||

{

|

||||

rt_kprintf("apply for 8MB memory fail ~!!!");

|

||||

}

|

||||

else

|

||||

{

|

||||

rt_kprintf("appyle for 8MB memory success!!!");

|

||||

}

|

||||

rt_free(p);

|

||||

}

|

||||

MSH_CMD_EXPORT(sram_test2, sram test2);

|

||||

#endif

|

||||

216

Ubiquitous/RT_Thread/aiit_board/xidatong/board/Kconfig

Normal file

216

Ubiquitous/RT_Thread/aiit_board/xidatong/board/Kconfig

Normal file

@@ -0,0 +1,216 @@

|

||||

menu "Hardware Drivers Config"

|

||||

|

||||

config SOC_IMXRT1052CVL5B

|

||||

bool

|

||||

select SOC_MIMXRT1050_SERIES

|

||||

select RT_USING_COMPONENTS_INIT

|

||||

select RT_USING_USER_MAIN

|

||||

default y

|

||||

|

||||

menu "On-chip Peripheral Drivers"

|

||||

|

||||

config BSP_USING_BOOT_IMAGE

|

||||

bool "Enable boot image"

|

||||

default y

|

||||

config BSP_USING_DMA

|

||||

bool "Enable DMA"

|

||||

default n

|

||||

|

||||

config BSP_USING_GPIO

|

||||

bool "Enable GPIO"

|

||||

select RT_USING_PIN

|

||||

default y

|

||||

menuconfig BSP_USING_LPUART

|

||||

bool "Enable UART"

|

||||

select RT_USING_SERIAL

|

||||

default y

|

||||

|

||||

if BSP_USING_LPUART

|

||||

config BSP_USING_LPUART1

|

||||

bool "Enable LPUART1"

|

||||

default y

|

||||

|

||||

config BSP_LPUART1_RX_USING_DMA

|

||||

bool "Enable LPUART1 RX DMA"

|

||||

depends on BSP_USING_LPUART1

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART1_RX_DMA_CHANNEL

|

||||

depends on BSP_LPUART1_RX_USING_DMA

|

||||

int "Set LPUART1 RX DMA channel (0-32)"

|

||||

default 0

|

||||

|

||||

config BSP_LPUART1_TX_USING_DMA

|

||||

bool "Enable LPUART1 TX DMA"

|

||||

depends on BSP_USING_LPUART1

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART1_TX_DMA_CHANNEL

|

||||

depends on BSP_LPUART1_TX_USING_DMA

|

||||

int "Set LPUART1 TX DMA channel (0-32)"

|

||||

default 1

|

||||

|

||||

config BSP_USING_LPUART2

|

||||

bool "Enable LPUART2"

|

||||

default y

|

||||

|

||||

config BSP_LPUART2_RX_USING_DMA

|

||||

bool "Enable LPUART2 RX DMA"

|

||||

depends on BSP_USING_LPUART2

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART2_RX_DMA_CHANNEL

|

||||

depends on BSP_LPUART2_RX_USING_DMA

|

||||

int "Set LPUART2 RX DMA channel (0-32)"

|

||||

default 2

|

||||

|

||||

config BSP_LPUART2_TX_USING_DMA

|

||||

bool "Enable LPUART2 TX DMA"

|

||||

depends on BSP_USING_LPUART2

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART2_TX_DMA_CHANNEL

|

||||

depends on BSP_LPUART2_TX_USING_DMA

|

||||

int "Set LPUART2 TX DMA channel (0-32)"

|

||||

default 3

|

||||

|

||||

config BSP_USING_LPUART3

|

||||

bool "Enable LPUART3"

|

||||

default y

|

||||

|

||||

config BSP_LPUART3_RX_USING_DMA

|

||||

bool "Enable LPUART3 RX DMA"

|

||||

depends on BSP_USING_LPUART3

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART3_RX_DMA_CHANNEL

|

||||

depends on BSP_LPUART3_RX_USING_DMA

|

||||

int "Set LPUART3 RX DMA channel (0-32)"

|

||||

default 4

|

||||

|

||||

config BSP_LPUART3_TX_USING_DMA

|

||||

bool "Enable LPUART3 TX DMA"

|

||||

depends on BSP_USING_LPUART3

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART3_TX_DMA_CHANNEL

|

||||

depends on BSP_LPUART3_TX_USING_DMA

|

||||

int "Set LPUART3 TX DMA channel (0-32)"

|

||||

default 5

|

||||

|

||||

config BSP_USING_LPUART4

|

||||

bool "Enable LPUART4"

|

||||

default n

|

||||

|

||||

config BSP_LPUART4_RX_USING_DMA

|

||||

bool "Enable LPUART4 RX DMA"

|

||||

depends on BSP_USING_LPUART4

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART4_RX_DMA_CHANNEL

|

||||

depends on BSP_LPUART4_RX_USING_DMA

|

||||

int "Set LPUART4 RX DMA channel (0-32)"

|

||||

default 6

|

||||

|

||||

config BSP_LPUART4_TX_USING_DMA

|

||||

bool "Enable LPUART4 TX DMA"

|

||||

depends on BSP_USING_LPUART4

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART4_TX_DMA_CHANNEL

|

||||

depends on BSP_LPUART4_TX_USING_DMA

|

||||

int "Set LPUART4 TX DMA channel (0-32)"

|

||||

default 7

|

||||

|

||||

|

||||

config BSP_USING_LPUART8

|

||||

bool "Enable LPUART8"

|

||||

default y

|

||||

|

||||

config BSP_LPUART8_RX_USING_DMA

|

||||

bool "Enable LPUART8 RX DMA"

|

||||

depends on BSP_USING_LPUART8

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART8_RX_DMA_CHANNEL

|

||||

depends on BSP_LPUART8_RX_USING_DMA

|

||||

int "Set LPUART8 RX DMA channel (0-32)"

|

||||

default 8

|

||||

|

||||

config BSP_LPUART8_TX_USING_DMA

|

||||

bool "Enable LPUART8 TX DMA"

|

||||

depends on BSP_USING_LPUART8

|

||||

select BSP_USING_DMA

|

||||

select RT_SERIAL_USING_DMA

|

||||

default n

|

||||

|

||||

config BSP_LPUART8_TX_DMA_CHANNEL

|

||||

depends on BSP_LPUART8_TX_USING_DMA

|

||||

int "Set LPUART8 TX DMA channel (0-32)"

|

||||

default 9

|

||||

|

||||

endif

|

||||

menuconfig BSP_USING_I2C

|

||||

bool "Enable I2C"

|

||||

select RT_USING_I2C

|

||||

default n

|

||||

if BSP_USING_I2C

|

||||

config BSP_USING_I2C1

|

||||

bool "Enable I2C1"

|

||||

default n

|

||||

choice

|

||||

prompt "Select I2C1 badurate"

|

||||

default HW_I2C1_BADURATE_100kHZ

|

||||

|

||||

config HW_I2C1_BADURATE_100kHZ

|

||||

bool "Badurate 100kHZ"

|

||||

|

||||

config HW_I2C1_BADURATE_400kHZ

|

||||

bool "Badurate 400kHZ"

|

||||

endchoice

|

||||

endif

|

||||

|

||||

menuconfig BSP_USING_CAN

|

||||

bool "Enable CAN"

|

||||

select RT_USING_CAN

|

||||

default n

|

||||

|

||||

if BSP_USING_CAN

|

||||

config BSP_USING_CAN1

|

||||

bool "Enable CAN1"

|

||||

default y

|

||||

endif

|

||||

|

||||

config BSP_USING_RTC

|

||||

bool "Enable RTC"

|

||||

select RT_USING_RTC

|

||||

default n

|

||||

|

||||

endmenu

|

||||

|

||||

menu "Onboard Peripheral Drivers"

|

||||

config BSP_USING_SDRAM

|

||||

bool "Enable SDRAM"

|

||||

default n

|

||||

endmenu

|

||||

|

||||

|

||||

endmenu

|

||||

@@ -0,0 +1,468 @@

|

||||

<?xml version="1.0" encoding= "UTF-8" ?>

|

||||

<configuration name="IMXRT1050-EVKB" version="1.5" xsi:schemaLocation="http://mcuxpresso.nxp.com/XSD/mex_configuration_1.5 http://mcuxpresso.nxp.com/XSD/mex_configuration_1.5.xsd" uuid="789fd1d3-821c-40a6-b04d-44ccc5a5d158" xmlns="http://mcuxpresso.nxp.com/XSD/mex_configuration_1.5" xmlns:xsi="http://www.w3.org/2001/XMLSchema-instance">

|

||||

<common>

|

||||

<processor>MIMXRT1052xxxxB</processor>

|

||||

<package>MIMXRT1052DVL6B</package>

|

||||

<board>IMXRT1050-EVKB</board>

|

||||

<board_revision>A</board_revision>

|

||||

<mcu_data>ksdk2_0</mcu_data>

|

||||

<cores selected="core0">

|

||||

<core name="Cortex-M7F" id="core0" description="M7 core"/>

|

||||

</cores>

|

||||

<description></description>

|

||||

</common>

|

||||

<preferences>

|

||||

<validate_boot_init_only>false</validate_boot_init_only>

|

||||

<generate_extended_information>false</generate_extended_information>

|

||||

</preferences>

|

||||

<tools>

|

||||

<pins name="Pins" version="5.0" enabled="true" update_project_code="true">

|

||||

<pins_profile>

|

||||

<processor_version>5.0.2</processor_version>

|

||||

<power_domains/>

|

||||

<pin_labels>

|

||||

<pin_label pin_num="G11" pin_signal="GPIO_AD_B0_03" label="BSP_BEEP"/>

|

||||

<pin_label pin_num="L13" pin_signal="GPIO_AD_B1_10" label="BSP_RS485_RE" identifier="CSI_D7"/>

|

||||

<pin_label pin_num="J13" pin_signal="GPIO_AD_B1_11" label="BSP_DS18B20" identifier="CSI_D6"/>

|

||||

<pin_label pin_num="K12" pin_signal="GPIO_AD_B1_05" label="BSP_AP3216C_INT" identifier="CSI_MCLK"/>

|

||||

</pin_labels>

|

||||

</pins_profile>

|

||||

<functions_list>

|

||||

<function name="BOARD_InitPins">

|

||||

<description>Configures pin routing and optionally pin electrical features.</description>

|

||||

<options>

|

||||

<callFromInitBoot>false</callFromInitBoot>

|

||||

<coreID>core0</coreID>

|

||||

<enableClock>true</enableClock>

|

||||

</options>

|

||||

<dependencies>

|

||||

<dependency resourceType="Peripheral" resourceId="LPUART1" description="Peripheral LPUART1 is not initialized" problem_level="1" source="Pins:BOARD_InitPins">

|

||||

<feature name="initialized" evaluation="equal">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="Peripheral" resourceId="LPUART2" description="Peripheral LPUART2 is not initialized" problem_level="1" source="Pins:BOARD_InitPins">

|

||||

<feature name="initialized" evaluation="equal">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="Peripheral" resourceId="LPUART5" description="Peripheral LPUART5 is not initialized" problem_level="1" source="Pins:BOARD_InitPins">

|

||||

<feature name="initialized" evaluation="equal">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="Peripheral" resourceId="PWM4" description="Peripheral PWM4 is not initialized" problem_level="1" source="Pins:BOARD_InitPins">

|

||||

<feature name="initialized" evaluation="equal">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="Peripheral" resourceId="PWM1" description="Peripheral PWM1 is not initialized" problem_level="1" source="Pins:BOARD_InitPins">

|

||||

<feature name="initialized" evaluation="equal">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="Peripheral" resourceId="LPI2C1" description="Peripheral LPI2C1 is not initialized" problem_level="1" source="Pins:BOARD_InitPins">

|

||||

<feature name="initialized" evaluation="equal">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.common" description="Pins initialization requires the COMMON Driver in the project." problem_level="2" source="Pins:BOARD_InitPins">

|

||||

<feature name="enabled" evaluation="equal" configuration="core0">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.iomuxc" description="Pins initialization requires the IOMUXC Driver in the project." problem_level="2" source="Pins:BOARD_InitPins">

|

||||

<feature name="enabled" evaluation="equal" configuration="core0">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

</dependencies>

|

||||

<pins>

|

||||

<pin peripheral="LPUART1" signal="TX" pin_num="K14" pin_signal="GPIO_AD_B0_12"/>

|

||||

<pin peripheral="LPUART1" signal="RX" pin_num="L14" pin_signal="GPIO_AD_B0_13"/>

|

||||

<pin peripheral="LPUART2" signal="TX" pin_num="L11" pin_signal="GPIO_AD_B1_02"/>

|

||||

<pin peripheral="LPUART2" signal="RX" pin_num="M12" pin_signal="GPIO_AD_B1_03"/>

|

||||

<pin peripheral="LPUART5" signal="TX" pin_num="D13" pin_signal="GPIO_B1_12"/>

|

||||

<pin peripheral="LPUART5" signal="RX" pin_num="D14" pin_signal="GPIO_B1_13"/>

|

||||

<pin peripheral="PWM4" signal="A, 0" pin_num="H13" pin_signal="GPIO_AD_B1_08"/>

|

||||

<pin peripheral="PWM4" signal="A, 1" pin_num="M13" pin_signal="GPIO_AD_B1_09"/>

|

||||

<pin peripheral="PWM1" signal="A, 3" pin_num="G13" pin_signal="GPIO_AD_B0_10"/>

|

||||

<pin peripheral="LPI2C1" signal="SCL" pin_num="J11" pin_signal="GPIO_AD_B1_00">

|

||||

<pin_features>

|

||||

<pin_feature name="software_input_on" value="Enable"/>

|

||||

</pin_features>

|

||||

</pin>

|

||||

<pin peripheral="LPI2C1" signal="SDA" pin_num="K11" pin_signal="GPIO_AD_B1_01">

|

||||

<pin_features>

|

||||

<pin_feature name="software_input_on" value="Enable"/>

|

||||

</pin_features>

|

||||

</pin>

|

||||

<pin peripheral="GPIO1" signal="gpio_io, 26" pin_num="L13" pin_signal="GPIO_AD_B1_10"/>

|

||||

<pin peripheral="GPIO1" signal="gpio_io, 03" pin_num="G11" pin_signal="GPIO_AD_B0_03"/>

|

||||

<pin peripheral="GPIO1" signal="gpio_io, 27" pin_num="J13" pin_signal="GPIO_AD_B1_11"/>

|

||||

<pin peripheral="GPIO1" signal="gpio_io, 21" pin_num="K12" pin_signal="GPIO_AD_B1_05"/>

|

||||

</pins>

|

||||

</function>

|

||||

</functions_list>

|

||||

</pins>

|

||||

<clocks name="Clocks" version="5.0" enabled="true" update_project_code="true">

|

||||

<clocks_profile>

|

||||

<processor_version>5.0.2</processor_version>

|

||||

</clocks_profile>

|

||||

<clock_configurations>

|

||||

<clock_configuration name="BOARD_BootClockRUN">

|

||||

<description></description>

|

||||

<options/>

|

||||

<dependencies>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.rtc_xtali" description="'RTC_XTALI' (Pins tool id: XTALOSC24M.rtc_xtali, Clocks tool id: XTALOSC24M.RTC_XTALI) needs to be routed" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="routed" evaluation="">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.rtc_xtali" description="'RTC_XTALI' (Pins tool id: XTALOSC24M.rtc_xtali, Clocks tool id: XTALOSC24M.RTC_XTALI) needs to have 'INPUT' direction" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="direction" evaluation="">

|

||||

<data>INPUT</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.rtc_xtalo" description="'RTC_XTALO' (Pins tool id: XTALOSC24M.rtc_xtalo, Clocks tool id: XTALOSC24M.RTC_XTALO) needs to be routed" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="routed" evaluation="">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.rtc_xtalo" description="'RTC_XTALO' (Pins tool id: XTALOSC24M.rtc_xtalo, Clocks tool id: XTALOSC24M.RTC_XTALO) needs to have 'OUTPUT' direction" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="direction" evaluation="">

|

||||

<data>OUTPUT</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.xtali" description="'XTALI' (Pins tool id: XTALOSC24M.xtali, Clocks tool id: XTALOSC24M.XTALI) needs to be routed" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="routed" evaluation="">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.xtali" description="'XTALI' (Pins tool id: XTALOSC24M.xtali, Clocks tool id: XTALOSC24M.XTALI) needs to have 'INPUT' direction" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="direction" evaluation="">

|

||||

<data>INPUT</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.xtalo" description="'XTALO' (Pins tool id: XTALOSC24M.xtalo, Clocks tool id: XTALOSC24M.XTALO) needs to be routed" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="routed" evaluation="">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PinSignal" resourceId="XTALOSC24M.xtalo" description="'XTALO' (Pins tool id: XTALOSC24M.xtalo, Clocks tool id: XTALOSC24M.XTALO) needs to have 'OUTPUT' direction" problem_level="1" source="Clocks:BOARD_BootClockRUN">

|

||||

<feature name="direction" evaluation="">

|

||||

<data>OUTPUT</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.common" description="Clocks initialization requires the COMMON Driver in the project." problem_level="2" source="Clocks.BOARD_BootClockRUN">

|

||||

<feature name="enabled" evaluation="equal" configuration="core0">

|

||||

<data>true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

</dependencies>

|

||||

<clock_sources>

|

||||

<clock_source id="XTALOSC24M.OSC.outFreq" value="24 MHz" locked="false" enabled="true"/>

|

||||

<clock_source id="XTALOSC24M.RTC_OSC.outFreq" value="32.768 kHz" locked="false" enabled="true"/>

|

||||

</clock_sources>

|

||||

<clock_outputs>

|

||||

<clock_output id="AHB_CLK_ROOT.outFreq" value="600 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="CAN_CLK_ROOT.outFreq" value="40 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="CKIL_SYNC_CLK_ROOT.outFreq" value="32.768 kHz" locked="false" accuracy=""/>

|

||||

<clock_output id="CLK_1M.outFreq" value="1 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="CLK_24M.outFreq" value="24 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="CSI_CLK_ROOT.outFreq" value="12 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="ENET1_TX_CLK.outFreq" value="2.4 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="ENET_125M_CLK.outFreq" value="2.4 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="ENET_25M_REF_CLK.outFreq" value="1.2 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="FLEXIO1_CLK_ROOT.outFreq" value="30 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="FLEXIO2_CLK_ROOT.outFreq" value="30 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="FLEXSPI_CLK_ROOT.outFreq" value="2880/11 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="GPT1_ipg_clk_highfreq.outFreq" value="75 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="GPT2_ipg_clk_highfreq.outFreq" value="75 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="IPG_CLK_ROOT.outFreq" value="150 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="LCDIF_CLK_ROOT.outFreq" value="67.5/7 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="LPI2C_CLK_ROOT.outFreq" value="60 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="LPSPI_CLK_ROOT.outFreq" value="105.6 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="LVDS1_CLK.outFreq" value="1.2 GHz" locked="false" accuracy=""/>

|

||||

<clock_output id="MQS_MCLK.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="PERCLK_CLK_ROOT.outFreq" value="75 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="PLL7_MAIN_CLK.outFreq" value="24 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI1_CLK_ROOT.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI1_MCLK1.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI1_MCLK2.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI1_MCLK3.outFreq" value="30 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI2_CLK_ROOT.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI2_MCLK1.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI2_MCLK3.outFreq" value="30 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI3_CLK_ROOT.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI3_MCLK1.outFreq" value="1080/17 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SAI3_MCLK3.outFreq" value="30 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SEMC_CLK_ROOT.outFreq" value="75 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="SPDIF0_CLK_ROOT.outFreq" value="30 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="TRACE_CLK_ROOT.outFreq" value="352/3 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="UART_CLK_ROOT.outFreq" value="80 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="USDHC1_CLK_ROOT.outFreq" value="198 MHz" locked="false" accuracy=""/>

|

||||

<clock_output id="USDHC2_CLK_ROOT.outFreq" value="198 MHz" locked="false" accuracy=""/>

|

||||

</clock_outputs>

|

||||

<clock_settings>

|

||||

<setting id="CCM.AHB_PODF.scale" value="1" locked="true"/>

|

||||

<setting id="CCM.ARM_PODF.scale" value="2" locked="true"/>

|

||||

<setting id="CCM.FLEXSPI_PODF.scale" value="1" locked="true"/>

|

||||

<setting id="CCM.FLEXSPI_SEL.sel" value="CCM_ANALOG.PLL3_PFD0_CLK" locked="false"/>

|

||||

<setting id="CCM.LCDIF_PODF.scale" value="8" locked="true"/>

|

||||

<setting id="CCM.LCDIF_PRED.scale" value="7" locked="true"/>

|

||||

<setting id="CCM.LPSPI_PODF.scale" value="5" locked="true"/>

|

||||

<setting id="CCM.PERCLK_PODF.scale" value="2" locked="true"/>

|

||||

<setting id="CCM.SEMC_PODF.scale" value="8" locked="false"/>

|

||||

<setting id="CCM.TRACE_PODF.scale" value="3" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL1_BYPASS.sel" value="CCM_ANALOG.PLL1" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL1_PREDIV.scale" value="1" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL1_VDIV.scale" value="50" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL2.denom" value="1" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL2.num" value="0" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL2_BYPASS.sel" value="CCM_ANALOG.PLL2_OUT_CLK" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL2_PFD0_BYPASS.sel" value="CCM_ANALOG.PLL2_PFD0" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL2_PFD1_BYPASS.sel" value="CCM_ANALOG.PLL2_PFD1" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL2_PFD2_BYPASS.sel" value="CCM_ANALOG.PLL2_PFD2" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL2_PFD3_BYPASS.sel" value="CCM_ANALOG.PLL2_PFD3" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL3_BYPASS.sel" value="CCM_ANALOG.PLL3" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL3_PFD0_BYPASS.sel" value="CCM_ANALOG.PLL3_PFD0" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL3_PFD0_DIV.scale" value="33" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL3_PFD0_MUL.scale" value="18" locked="true"/>

|

||||

<setting id="CCM_ANALOG.PLL3_PFD1_BYPASS.sel" value="CCM_ANALOG.PLL3_PFD1" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL3_PFD2_BYPASS.sel" value="CCM_ANALOG.PLL3_PFD2" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL3_PFD3_BYPASS.sel" value="CCM_ANALOG.PLL3_PFD3" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL4.denom" value="50" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL4.div" value="47" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL5.denom" value="1" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL5.div" value="40" locked="false"/>

|

||||

<setting id="CCM_ANALOG.PLL5.num" value="0" locked="false"/>

|

||||

<setting id="CCM_ANALOG_PLL_ENET_POWERDOWN_CFG" value="Yes" locked="false"/>

|

||||

<setting id="CCM_ANALOG_PLL_USB1_POWER_CFG" value="Yes" locked="false"/>

|

||||

</clock_settings>

|

||||

<called_from_default_init>true</called_from_default_init>

|

||||

</clock_configuration>

|

||||

</clock_configurations>

|

||||

</clocks>

|

||||

<periphs name="Peripherals" version="5.0" enabled="true" update_project_code="true">

|

||||

<dependencies>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.lpuart" description="在工具链/IDE工程中未发现LPUART Driver。" problem_level="2" source="Peripherals">

|

||||

<feature name="enabled" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.lpuart" description="工具链/IDE工程中LPUART Driver不被支持的版本。需要:${required_value},实际:${actual_value}。" problem_level="1" source="Peripherals">

|

||||

<feature name="version" evaluation="equivalent">

|

||||

<data type="Version">2.2.4</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.lpi2c" description="在工具链/IDE工程中未发现LPI2C Driver。" problem_level="2" source="Peripherals">

|

||||

<feature name="enabled" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="SWComponent" resourceId="platform.drivers.lpi2c" description="工具链/IDE工程中LPI2C Driver不被支持的版本。需要:${required_value},实际:${actual_value}。" problem_level="1" source="Peripherals">

|

||||

<feature name="version" evaluation="equivalent">

|

||||

<data type="Version">2.1.5</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

</dependencies>

|

||||

<peripherals_profile>

|

||||

<processor_version>5.0.2</processor_version>

|

||||

</peripherals_profile>

|

||||

<functional_groups>

|

||||

<functional_group name="BOARD_InitPeripherals" uuid="a7525270-2da6-4556-8d91-4ab9d0edc0e2" called_from_default_init="true" id_prefix="" core="core0">

|

||||

<description></description>

|

||||

<options/>

|

||||

<dependencies>

|

||||

<dependency resourceType="ClockOutput" resourceId="UART_CLK_ROOT" description="UART_CLK_ROOT is inactive." problem_level="2" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="frequency" evaluation="greaterThan">

|

||||

<data type="Frequency" unit="Hz">0</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPUART1.uart_tx" description="Signal TX of the peripheral LPUART1 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPUART1.uart_rx" description="Signal RX of the peripheral LPUART1 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="ClockOutput" resourceId="LPI2C_CLK_ROOT" description="LPI2C_CLK_ROOT is inactive." problem_level="2" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="frequency" evaluation="greaterThan">

|

||||

<data type="Frequency" unit="Hz">0</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPI2C1.lpi2c_scl" description="Signal serial clock of the peripheral LPI2C1 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPI2C1.lpi2c_sda" description="Signal serial data of the peripheral LPI2C1 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="ClockOutput" resourceId="UART_CLK_ROOT" description="UART_CLK_ROOT is inactive." problem_level="2" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="frequency" evaluation="greaterThan">

|

||||

<data type="Frequency" unit="Hz">0</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPUART2.uart_tx" description="Signal TX of the peripheral LPUART2 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPUART2.uart_rx" description="Signal RX of the peripheral LPUART2 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="ClockOutput" resourceId="UART_CLK_ROOT" description="UART_CLK_ROOT is inactive." problem_level="2" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="frequency" evaluation="greaterThan">

|

||||

<data type="Frequency" unit="Hz">0</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPUART5.uart_tx" description="Signal TX of the peripheral LPUART5 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

<dependency resourceType="PeripheralUnifiedSignal" resourceId="LPUART5.uart_rx" description="Signal RX of the peripheral LPUART5 is not routed." problem_level="1" source="Peripherals:BOARD_InitPeripherals">

|

||||

<feature name="routed" evaluation="equal">

|

||||

<data type="Boolean">true</data>

|

||||

</feature>

|

||||

</dependency>

|

||||

</dependencies>

|

||||

<instances>

|

||||

<instance name="LPUART_1" type="lpuart" type_id="lpuart_bebe3e12b6ec22bbd14199038f2bf459" mode="polling" peripheral="LPUART1" enabled="true">

|

||||

<config_set name="lpuartConfig_t" quick_selection="QuickSelection1">

|

||||

<struct name="lpuartConfig">

|

||||

<setting name="clockSource" value="LpuartClock"/>

|

||||

<setting name="lpuartSrcClkFreq" value="BOARD_BootClockRUN"/>

|

||||

<setting name="baudRate_Bps" value="115200"/>

|

||||

<setting name="parityMode" value="kLPUART_ParityDisabled"/>

|

||||

<setting name="dataBitsCount" value="kLPUART_EightDataBits"/>

|

||||

<setting name="isMsb" value="false"/>

|

||||

<setting name="stopBitCount" value="kLPUART_OneStopBit"/>

|

||||

<setting name="txFifoWatermark" value="0"/>

|

||||

<setting name="rxFifoWatermark" value="1"/>

|

||||

<setting name="enableRxRTS" value="false"/>

|

||||

<setting name="enableTxCTS" value="false"/>

|

||||

<setting name="txCtsSource" value="kLPUART_CtsSourcePin"/>

|

||||

<setting name="txCtsConfig" value="kLPUART_CtsSampleAtStart"/>

|

||||

<setting name="rxIdleType" value="kLPUART_IdleTypeStartBit"/>

|

||||

<setting name="rxIdleConfig" value="kLPUART_IdleCharacter1"/>

|

||||

<setting name="enableTx" value="true"/>

|

||||

<setting name="enableRx" value="true"/>

|

||||

</struct>

|

||||

</config_set>

|

||||

</instance>

|

||||

<instance name="LPI2C_1" type="lpi2c" type_id="lpi2c_db68d4f4f06a22e25ab51fe9bd6db4d2" mode="master" peripheral="LPI2C1" enabled="true">

|

||||

<config_set name="main" quick_selection="qs_interrupt">

|

||||

<setting name="clockSource" value="Lpi2cClock"/>

|

||||

<setting name="clockSourceFreq" value="BOARD_BootClockRUN"/>

|

||||

<struct name="interrupt">

|

||||

<setting name="IRQn" value="LPI2C1_IRQn"/>

|

||||

<setting name="enable_priority" value="false"/>

|

||||

<setting name="enable_custom_name" value="false"/>

|

||||

</struct>

|

||||

</config_set>

|

||||

<config_set name="master" quick_selection="qs_master_transfer">

|

||||

<setting name="mode" value="transfer"/>

|

||||

<struct name="config">

|

||||

<setting name="enableMaster" value="true"/>

|

||||

<setting name="enableDoze" value="true"/>

|

||||

<setting name="debugEnable" value="false"/>

|

||||

<setting name="ignoreAck" value="false"/>

|

||||

<setting name="pinConfig" value="kLPI2C_2PinOpenDrain"/>

|

||||

<setting name="baudRate_Hz" value="100000"/>

|

||||

<setting name="busIdleTimeout_ns" value="0"/>

|

||||

<setting name="pinLowTimeout_ns" value="0"/>

|

||||

<setting name="sdaGlitchFilterWidth_ns" value="0"/>

|

||||

<setting name="sclGlitchFilterWidth_ns" value="0"/>

|

||||

<struct name="hostRequest">

|

||||

<setting name="enable" value="false"/>

|

||||

<setting name="source" value="kLPI2C_HostRequestExternalPin"/>

|

||||

<setting name="polarity" value="kLPI2C_HostRequestPinActiveHigh"/>

|

||||

</struct>

|

||||

</struct>

|

||||

<struct name="transfer">

|

||||

<setting name="blocking" value="false"/>

|

||||

<set name="flags">

|

||||

<selected/>

|

||||

</set>

|

||||

<setting name="slaveAddress" value="0"/>

|

||||

<setting name="direction" value="kLPI2C_Write"/>

|

||||

<setting name="subaddress" value="0"/>

|

||||

<setting name="subaddressSize" value="1"/>

|

||||

<setting name="dataSize" value="1"/>

|

||||

<struct name="callback">

|

||||

<setting name="name" value=""/>

|

||||

<setting name="userData" value=""/>

|

||||

</struct>

|

||||

</struct>

|

||||

</config_set>

|

||||

</instance>

|

||||

<instance name="LPUART_2" type="lpuart" type_id="lpuart_bebe3e12b6ec22bbd14199038f2bf459" mode="polling" peripheral="LPUART2" enabled="true">

|

||||

<config_set name="lpuartConfig_t" quick_selection="QuickSelection1">

|

||||

<struct name="lpuartConfig">

|

||||

<setting name="clockSource" value="LpuartClock"/>

|

||||

<setting name="lpuartSrcClkFreq" value="BOARD_BootClockRUN"/>

|

||||

<setting name="baudRate_Bps" value="115200"/>

|

||||

<setting name="parityMode" value="kLPUART_ParityDisabled"/>

|

||||

<setting name="dataBitsCount" value="kLPUART_EightDataBits"/>

|

||||

<setting name="isMsb" value="false"/>

|

||||

<setting name="stopBitCount" value="kLPUART_OneStopBit"/>

|

||||

<setting name="txFifoWatermark" value="0"/>

|

||||

<setting name="rxFifoWatermark" value="1"/>

|

||||

<setting name="enableRxRTS" value="false"/>

|

||||

<setting name="enableTxCTS" value="false"/>

|

||||

<setting name="txCtsSource" value="kLPUART_CtsSourcePin"/>

|

||||

<setting name="txCtsConfig" value="kLPUART_CtsSampleAtStart"/>

|

||||

<setting name="rxIdleType" value="kLPUART_IdleTypeStartBit"/>

|

||||

<setting name="rxIdleConfig" value="kLPUART_IdleCharacter1"/>

|

||||

<setting name="enableTx" value="true"/>

|

||||

<setting name="enableRx" value="true"/>

|

||||

</struct>

|

||||

</config_set>

|

||||

</instance>

|

||||

<instance name="LPUART_3" type="lpuart" type_id="lpuart_bebe3e12b6ec22bbd14199038f2bf459" mode="polling" peripheral="LPUART5" enabled="true">

|

||||

<config_set name="lpuartConfig_t" quick_selection="QuickSelection1">

|

||||

<struct name="lpuartConfig">

|

||||

<setting name="clockSource" value="LpuartClock"/>

|

||||

<setting name="lpuartSrcClkFreq" value="BOARD_BootClockRUN"/>

|

||||

<setting name="baudRate_Bps" value="115200"/>

|

||||

<setting name="parityMode" value="kLPUART_ParityDisabled"/>

|

||||

<setting name="dataBitsCount" value="kLPUART_EightDataBits"/>

|

||||

<setting name="isMsb" value="false"/>

|

||||

<setting name="stopBitCount" value="kLPUART_OneStopBit"/>

|

||||

<setting name="txFifoWatermark" value="0"/>

|

||||

<setting name="rxFifoWatermark" value="1"/>

|

||||

<setting name="enableRxRTS" value="false"/>

|

||||

<setting name="enableTxCTS" value="false"/>

|

||||

<setting name="txCtsSource" value="kLPUART_CtsSourcePin"/>

|

||||

<setting name="txCtsConfig" value="kLPUART_CtsSampleAtStart"/>

|

||||

<setting name="rxIdleType" value="kLPUART_IdleTypeStartBit"/>

|

||||

<setting name="rxIdleConfig" value="kLPUART_IdleCharacter1"/>

|

||||

<setting name="enableTx" value="true"/>

|

||||

<setting name="enableRx" value="true"/>

|

||||

</struct>

|

||||

</config_set>

|

||||

</instance>

|

||||

</instances>

|

||||

</functional_group>

|

||||

</functional_groups>

|

||||

<components>

|

||||